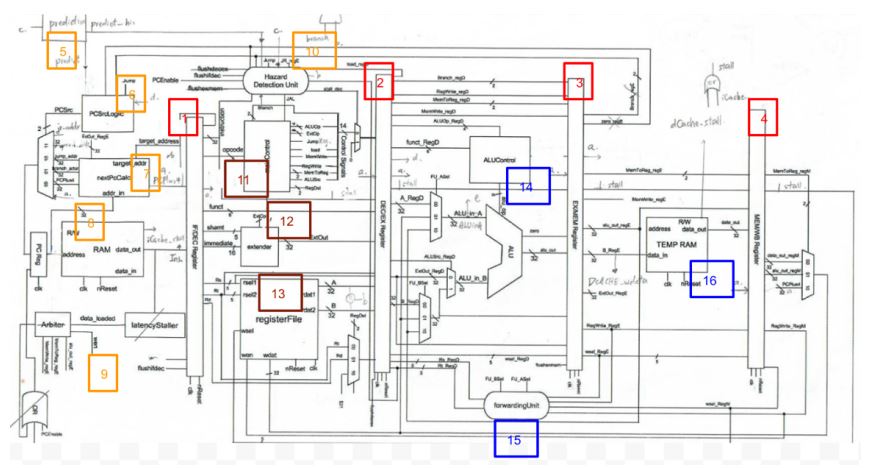

In this project, we implemented the MIPS CPU with pipeline architecture by Verilog code and managed to overcome data hazard, lw-use hazard, structural hazard, and control hazard. Besides, we extended the basic function by considering branch prediction, L1/L2 cache, and support of multiplication and division. We compared the performance of different implementations of branch prediction, namely, one-bit or two-bit. In addition, we discussed the advantages that L1/L2 cache brings about. In the final presentation, our work was awarded the second prize.